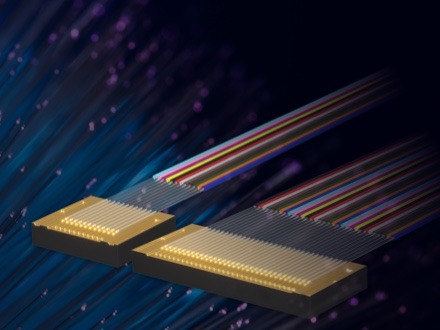

Co-Packaged Optics Fiber Connector with 32+ Fibers at 127µm Pitch

Teramount features its innovative detachable fiber connector to chip, supporting an industry-first 32+ SM/PM mix of fibers at 127µm pitch. Such fiber count and density enable unparalleled bandwidth density for Co-Packaged Optics (CPO).

The relentless pursuit of higher data rates, driven by AI/ML and HPC applications, has created tremendous strain on increasing data connectivity to chipsets while shrinking chipset sizes.

The CPO paradigm, brings fiber connectivity close to processors, helping to significantly reduce the power consumption of such processors, by shortening their electrical SerDes interfaces to a few millimeters, before connecting to a Photonic Integrated IC (PIC) and to fibers.

One of the big challenges of CPO however, is maintaining a high bandwidth density with fibers, to minimize the overall processor package size.

To get a sense of how big the problem is, next Generation 102.4 Tbps CPO-enabled switches will require over 2000 Single Mode (SM) fibers (in 400GBASE-DR4 schemes) and up to 500 PM fibers (for connecting external laser systems) spread across 16/32 PICs with a capacity of 6.4/3.2 Tbps respectively (64-128 SM fibers and 4/8 PM fibers per PIC).

Current fiber connectivity approaches typically connect a small number of fibers (~12-16) to SiPh chips at 250 µm pitch, which leads to very low bandwidth density – unsuitable for CPO packaging.

Increasing the bandwidth density with current approaches is doomed to fail for several reasons:

- Reducing the fiber pitch from 250 µm to 127 µm will cause the fibers to rest lower inside the V-Grooves, losing their core height alignment with the SiPh waveguides.

- Increasing the number of fibers/V-Grooves per PIC creates sensitivity in terms of fiber shifts due to thermal expansions in reflows and high-temperature operation, as well as sensitivity to wafer bowing, which again makes it very difficult to maintain fiber core alignment with the SiPh waveguides.

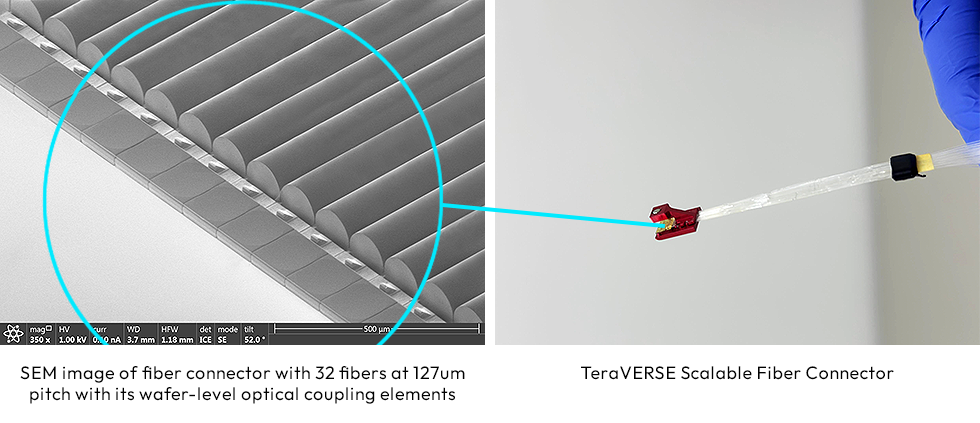

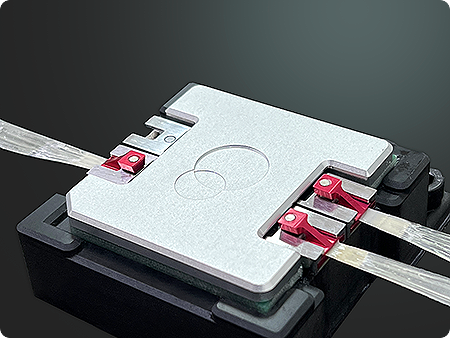

Teramount’s unique solution for fiber connectivity to SiPh chips, in the form of TeraVERSE® detachable fiber connector for CPO, overcomes all these challenges providing 127 µm fiber pitch, 32+ mix of SM/PM fibers in a single TeraVERSE connector and the ability to attach multiple such connectors to a single PIC using our modular socket design, making this a very scalable solution, able to support even the largest and densest PICs and processors.

TeraVERSE uses an innovative wideband surface coupling solution that relies on wafer-level manufacturing processes to create Teramount’s self-aligning optics scheme. This scheme generates unprecedented assembly tolerances, critical for enabling a fully passive, detachable large-scale fiber connector.

This planar separation of the fibers from the PIC/waveguides enables the dense fiber pitch and the large number of fibers to be used without PIC bowing or thermal shift concerns (as the fibers are connected to the PIC only after all reflows are done).

As the chase after ever-increasing demand for data capacity and rates is with no end in sight, bandwidth density becomes more and more of a problem that must be addressed for next-generation high-performance processors. Teramount’s TeraVERSE provides unparalleled bandwidth density, which can scale easily to meet current and future bandwidth demand.

Read more about Teramount’s technology Here.